Tri-State Buffers and Their Applications

How do complex microprocessor systems preserve the integrity of data buses?

Understanding Tri-State Buffers

A Tri-State Buffer is a digital component that has 3 stable output states -

- High (Logic 1)

- Low (Logic 0)

- High-Impedance (Hi-Z)

While the buffer behaves like a standard logic buffer in the High and Low states, it enters a Hi-Z state when deactivated, effectively disconnecting the output from the circuit.

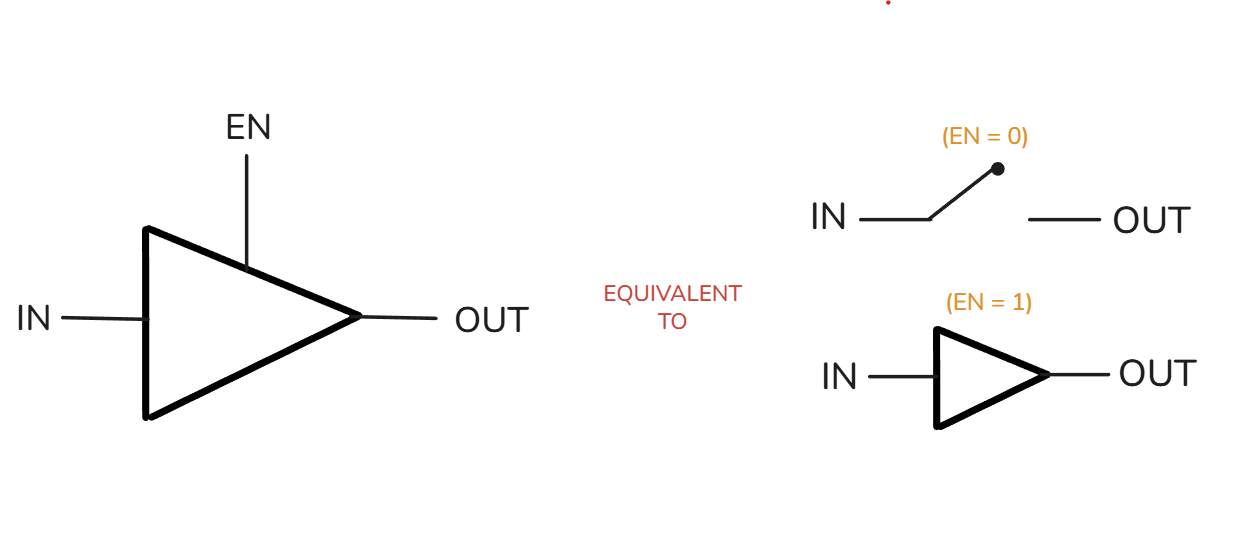

The diagram above shows a Tri-State Buffer with an Active-High Tri-State Enable (EN) signal. The buffer is equivalent to an "open circuit" when the EN signal is de-asserted. When EN is asserted, the Tri-State buffer behaves like a "normal buffer", passing the input signal to the output.

Applications of Tri-State Buffers

- Arbitration in Computer Systems

Tri-State Buffers are commonly used in systems where multiple devices are connected to the same shared resource.

For example, in a microprocessor based system, the CPU, the memory modules and the peripherals generally share the same data bus. To ensure that only one device can transmit on the bus at any given time, every device is equipped with a tri-state buffers. In the absence of Tri-State Buffers, multiple devices would transmit data at the same time, thereby causing bus contention. - Multiplexing in Digital Circuits

Tri-state buffers help implement efficient multiplexers, especially when multiple sources need to drive a single output line. Instead of using complex logic gates, tri-state buffers allow selective activation of inputs, reducing circuit complexity. - Bi-Directional Data Transfers

In bidirectional buses, such as those used in microcontrollers and memory interfaces, Tri-State buffers enable controlled data flow. For example, in an I²C or SPI bus, devices enter a high-impedance state when not transmitting, preventing interference. - Peripheral Device Control

Many peripheral devices, such as sensors and external memory modules, use Tri-State buffers to disconnect from the system when not in use. This prevents unnecessary power consumption and ensures only active devices drive the bus.

Tri-stating shared lines not in use provide an additional advantage of reducing crosstalk and noise on a bus.

Why Can’t a Device Just Drive 0 When Not in Use?

If an idle device drives a 0 instead of going Hi-Z, it still actively controls the bus. If another device attempts to transmit a 1, it creates a contention scenario, leading to:

- Erroneous data transfers

- Signal corruption

- Potential hardware damage in extreme cases

By using Tri-State Buffers, designers ensure efficient bus arbitration, proper data transmission, and safe signal handling across digital systems.